# Charge Domain Folding ADC for Multi-bit ΔΣ AD Modulator

Xiongyan Li<sup>1,a</sup>, Tianrui Feng<sup>1,b</sup>, Lengkhang Nengvang<sup>1,c</sup>, Haijun Lin<sup>2,d</sup>, Shogo Katayama<sup>1,e</sup>, Jianglin Wei<sup>1,f</sup>, Anna Kuwana<sup>1,g</sup>, Kazufumi Naganuma<sup>3,h</sup>, Kiyoshi Sasai<sup>3,i</sup>, Junichi Saito<sup>3,j</sup>, Katsuaki Morishita<sup>3,k</sup>, \*Haruo Kobayashi<sup>1,l</sup>

<sup>1</sup>Division of Electronics and Informatics, Faculty of Science and Technology, Gunma University, 1-5-1 Tenjin-cho, Kiryu, Gunma 376-8515, Japan

<sup>2</sup>Xiamen Institute of Technology, School of Optoelectronic and Communication Engineering, Xiamen University of Technology, 3610024, Xiamen City, China

<sup>3</sup>Alps Alpine Co., Ltd., 3-31 Ake-dori, Izumi-Ku, Sendai, Miyagi 981-3280, Japan

\*Corresponding author

a<t191d603@gunma-u.ac.jp>, b<t201d607@gunma-u.ac.jp>, c<t170d515@gunma-u.ac.jp>, d<linhaijun@xmut.edu.cn>, e<t15304906@gunma-u.ac.jp>, f<t192d601@gunma-u.ac.jp>, g<kuwana.anna@gunma-u.ac.jp>, h<kazufumi.naganuma@alpsalpine.com>, i<kiyoshi.sasai@alpsalpine.com>, j<junichi.saito@alpsalpine.com>, k<katsuaki.morishita@alpsalpine.com>, l<koba@gunma-u.ac.jp>

**Keywords:** folding ADC, ΔΣ ADC, multi-bit, charge domain, Leslie-Singh architecture

Abstract. This paper describes consideration on folding ADC usage inside a multi-bit  $\Delta\Sigma$  AD modulator. The folding ADC requires only one comparator for each bit with analog preprocessing circuits; hence, it requires only small hardware and its power consumption is small for 5-bit or 6-bit resolution. Further its latency is small (one or two clock cycles) compared to an SAR ADC or a pipelined ADC. We propose to use a 5-bit or 6-bit ADC and a 3-bit DAC inside the modulator. We consider that thanks to these characteristics, 5-bit or 6-bit  $\Delta\Sigma$  AD modulator can be implemented using the folding ADC. Also, our designed charge mode folding ADC employing discrete-time signal processing in Gray code output format is shown with SPICE simulation results using TSMC 0.18µm CMOS SPICE parameters. It may suffer from nonlinearity due to device mismatches, but it will be noise-shaped inside the modulator and its effects will be alleviated.

#### 1. Introduction

A multi-bit  $\Delta\Sigma$  AD modulator is attractive because the quantization noise of the ADC inside is reduced and the multi-bit DAC improves the high-order modulator loop stability as well as the integrator operational amplifier swing is reduced. Also, in a continuous-time modulator, the DAC clock jitter effects are alleviated. The multi-bit ADC inside the modulator improves the signal-to-[quantization noise + distortion] ratio (SQNDR) by 3 dB for 1-bit resolution increase [1]. In many cases, the resolution of the ADC inside the modulator is limited up-to 3-bit or at most 4-bit when the flash-type ADC architecture is employed. The 3-bit flash ADC uses 7 comparators while the 4-bit one uses 15 comparators. For the 5-bit flash one, 31 comparators are required and for the 6-bit one, 63 comparators are needed; these require relatively large hardware and consume a lot of power. When an SAR ADC is employed inside the modulator, high resolution can be realized with small hardware and power. However, its latency is long, which degrades the output rate of the modulator.

In this paper, usage of the folding ADC inside the multi-bit  $\Delta\Sigma$  AD modulator is investigated; even in the 6-bit resolution case, only 6 comparators with some analog encoding circuits are required and

its latency is only one or two clock cycles. Also, extension of the Leslie-Singh  $\Delta\Sigma$  modulator architecture [2, 3] is shown, which can employ e. g., a 6-bit folding ADC and a 3-bit DAC inside the modulator. In the 2nd or 3rd order modulator, a 3-bit DAC may be enough in many cases; more than 3-bit resolution DAC requires extra hardware and power without much benefits to the modulator. Further, as an example of the 5-bit folding ADC, the charge mode one is shown with its simulation results.

Our charge domain folding ADC uses switches and capacitors, which are suitable for CMOS implementation, and its preliminary ideas are shown in [4, 5]. There are other folding ADCs which uses switched capacitors [6, 7], but our folding ADC is different from them mainly because ours uses saturation or sigmoid characteristics of the pre-amplifier. Previously current domain folding ADC was developed for bipolar transistor implementation, because the bipolar transistor has good current driving capability [8], however recently its CMOS implementations as well as its design methodologies have been reported [9-21]. The advantages of our charge domain folding ADC are that there is very few additional hardware to realize analog encoding very fast without high frequency signal generation internally.

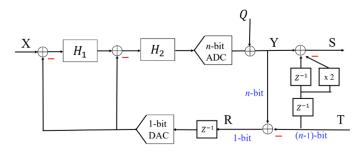

#### 2.1 Extension of Leslie-Singh Architecture

Leslie and Singh proposed a second-order  $\Delta\Sigma$  AD modulator in [2] which uses a multi-bit ADC and a single-bit DAC (Fig. 1), which can reduce the quantization noise of the ADC inside the modulator and avoid the nonlinearity of the DAC; it is because the single-bit DAC is inherently linear whereas the multi-bit DAC has some nonlinearities. However, the single-bit DAC usage sacrifices the advantages of the multi-bit DAC usage; the loop stability improvement and the integrator operational amplifier swing reduction, as well as the DAC jitter effect reduction in a continuous-time modulator.

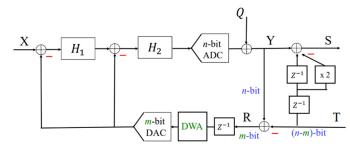

Hence, we investigate a  $\Delta\Sigma$  AD modulator which uses a 6-bit or 5-bit folding ADC and a 3-bit DAC with the data-weighted-averaging (DWA) algorithm logic, with the same structure as the Leslie-Singh architecture (Fig.2). The upper 3 bits of the 6-bit or 5-bit folding ADC are applied to the inputs of the 3-bit DAC with Data-Weighted Averaging (DWA) logic. This investigated structure would be well-balanced; the usage of a 6-bit DAC may lead to too much hardware and power with only small performance improvement, and the 3-bit DAC would suffice. Also see [32] in the 1<sup>st</sup>-order modulator case.

Fig. 1. Leslie-Singh 2nd-order  $\Delta\Sigma$  AD modulator with an *n*-bit ADC and a 1-bit DAC.

Fig. 2. Investigated 2nd-order  $\Delta\Sigma$  AD modulator with an *n*-bit ADC and an *m*-bit DAC (*n*>*m*).

In Figs. 1 and 2, we have the following:

$$[1 + Z^{-1}H_2(Z) [1 + H_1(Z)]] Y(Z)$$

$$= Q(Z) + H_2(Z)H_1(Z)X(Z) + Z^{-1}H_2(Z) [1 + H_1(Z)]T(Z)$$

(1)

Here, X(Z) is the input signal, Y(Z) is the n-bit ADC output, Q(Z) is the ADC quantization noise, and S(Z) is the modulator output. Here we consider the second-order modulator, and hence  $H_1(Z)$  and  $H_2(Z)$  are analog integrators, given by

$$H_1(Z) = \frac{1}{1-Z^{-1}}, \quad H_2(Z) = \frac{1}{1-Z^{-1}}.$$

(2)

T(Z) is the lower (n-m) bits of the n-bit ADC output, while R(Z) the upper m bits of the n-bit ADC output. In Fig. 1, m=1, and in Fig. 2, we consider n=5 or 6 and m=3. In other words, the internal m-bit DAC is driven by the upper m-bit of the n-bit ADC output. Then we have the followings:

$$Y(Z) = X(Z) + (1 - Z^{-1})^{2} Q(Z) + (-Z^{-2} + 2Z^{-1})T(Z)$$

(3)

By simple digital calculation, we have the modulator output:

$$S(Z) = Y(Z) + (-2Z^{-1} + Z^{-2})T(Z) = X(Z) + (1 - Z^{-1})^{2}Q(Z)$$

(4)

We see that the quantization noise Q(Z) is the second-order noise-shaped. Notice that S(Z) can be obtained from calculation of the ADC output Y(Z) and its lower (n-m)-bits T(Z) in a feedforward manner as shown in Eq. (4), it is not included in Eq. (1).

Note that the DWA logic in Fig. 2 is for the noise-shaping of the multi-bit (m-bit, m>1) nonlinearities [1, 33].

#### 2.2 Charge Mode Folding ADC

We describe here our charge mode folding ADC design with TSMC 0.18µm CMOS SPICE parameters and 3V supply voltage. Its circuit and SPICE simulation results are shown in this subsection. We have designed a 6-bit folding ADC but due to space limitation, only a 5-bit case is shown. The resolution of 6-bit can be easily realized with simple hardware.

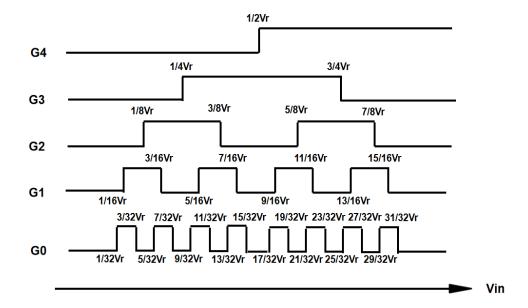

Its digital output is provided in Gray code format (Table 1, Fig. 3), and the Gray code can be converted to the binary code using exclusive OR (EXOR) gates; the 2-input EXOR gate can be realized with 2 PMOSFETs and 2 NMOSFETs [34].

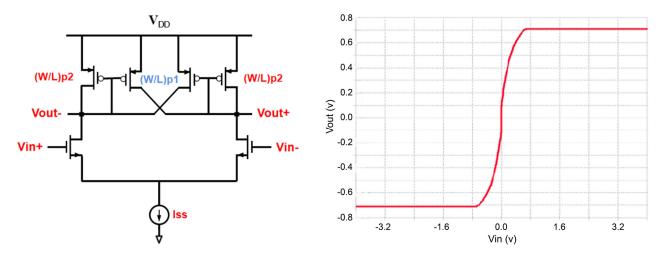

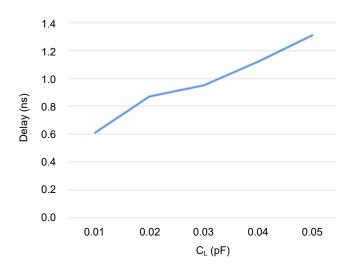

The preamplifier circuit and its SPICE simulation results are shown in Fig. 4. Preamplifier saturation characteristics is used and nonlinear switched capacitor folding circuit can be designed. In the preamplifier, the parameter of transistors as following:  $(W/L)_{input}=2\mu m/0.2\mu m$ ,  $(W/L)_{p1}=1.5\mu m/0.2\mu m$ ,  $(W/L)_{p2}=2\mu m/0.2\mu m$  and the tail current is  $50\mu A$ . We simulated the delay time of the preamplifier with load capacitance changes when current is  $50\mu A$  (Fig. 4 (c)), and tail current changes with 0.03pF load capacitance (Fig. 4 (d)). In the condition of 0.03pF load capacitance with  $50\mu A$ , the preamplifier has a 0.95ns delay time. Here the load capacitance is the one between Vout+ and ground and the one between Vout- and ground in Fig. 4 (a).

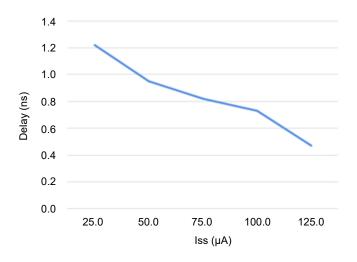

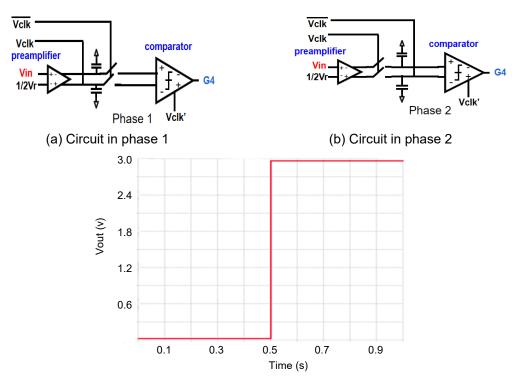

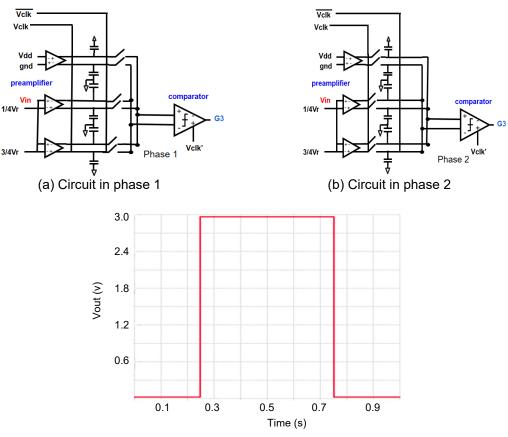

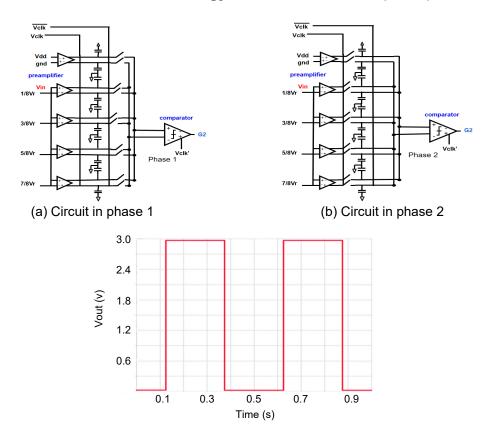

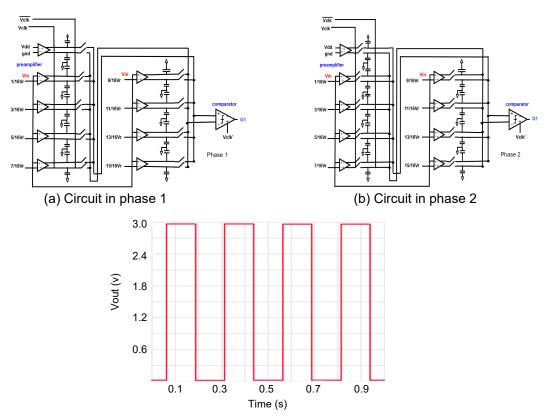

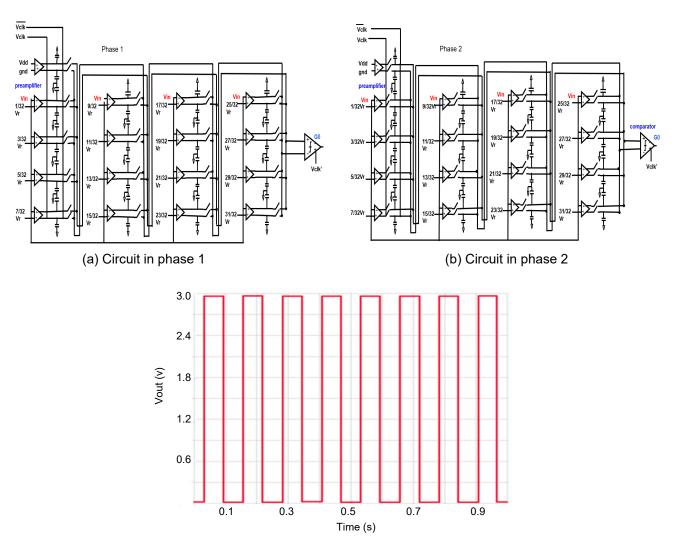

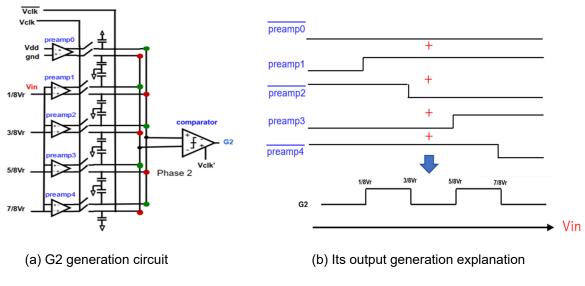

The circuit configurations, operations and SPICE simulation results for G4, G3, G2, G1, G0 generation are shown in Figs. 5, 6, 7, 8 and 9, respectively, where transient simulations were performed for the ramp input Vin. In phase 1, the output of each preamplifier is sampled and stored in each capacitor. In phase 2, the preamplifier output and the capacitor are disconnected. Then each capacitor is connected. Notice that the differential capacitor outputs are connected alternately (Fig. 10). Its analog encoding is done in charge domain and discrete-time, which is suitable for CMOS implementation. In

other words, analog encoding is done by just connection, and hence it reduces hardware and power significantly compared to the flash ADC.

This can avoid CMOS low current drivability. Its conversion latency is one or two-clock, which is comparable to the flash ADC. If this ADC is used stand alone, it may suffer from device mismatches such as preamplifier and comparator offsets, which lead to the whole  $\Delta\Sigma$  ADC nonlinearity. However, it is used inside the modulator, the nonlinearity is noise-shaped and does not affect the whole modulator linearity significantly (Fig. 10).

Also notice that in phase 1 the preamplifier tail current can be cut off for power reduction.

| Decimal number | Binary Code | Gray Code |

|----------------|-------------|-----------|

| 0              | 00000       | 00000     |

| 1              | 00001       | 00001     |

| 2              | 00010       | 00011     |

| 3              | 00011       | 00010     |

| 4              | 00100       | 00110     |

| 5              | 00101       | 00111     |

| 6              | 00110       | 00101     |

| 7              | 00111       | 00100     |

| 8              | 01000       | 01100     |

| 9              | 01001       | 01101     |

| 10             | 01010       | 01111     |

| 11             | 01011       | 01110     |

| 12             | 01100       | 01010     |

| 13             | 01101       | 01011     |

| 14             | 01110       | 01001     |

| 15             | 01111       | 01000     |

Table 1. Binary code and Gray code

Fig. 3. Gray code digital output with respect to the analog input Vin.

(a) Circuit configuration

(b) SPICE simulation results (ΔVout /ΔVin)

(c) Simulation results of delay time with load capacitance changes, where the tail current is  $50 \, \mu A$

(d) Simulation results of delay time with tail current changes, where the load capacitance is 0.03 pF

Fig. 4. Pre-amplifier circuit.

(c) SPICE transient simulation result for the ramp input

Fig. 5. MSB (G4) generation circuit of the proposed charge-domain folding ADC.

(c) SPICE transient simulation result for the ramp input

Fig. 6. MSB-1 (G3) generation circuit of the proposed charge-domain folding ADC.

(c) SPICE transient simulation result for the ramp input

Fig. 7. MSB-2 (G2) generation circuit of the proposed charge-domain folding ADC.

(c) SPICE transient simulation result for the ramp input

Fig. 8. MSB-3 (G1) generation circuit of the proposed charge-domain folding ADC.

(c) SPICE transient simulation result for the ramp input

Fig. 9. LSB (G0) generation circuit of the proposed charge-domain folding ADC.

Fig. 10. Explanation of analog encoding for G2 generation.

#### 3. Conclusion

In this paper, usage of the folding ADC inside the multi-bit  $\Delta\Sigma$  AD modulator is investigated; the 6-bit resolution ADC inside the modulator can be realized with small latency and small circuitry as well low power. Also, extension of the Leslie-Singh architecture is shown, which employs a 6-bit folding ADC and a 3-bit DAC with DWA inside the modulator. Finally, we remark that the folding ADC can be also used inside the pipelined ADC with the similar arguments as the contents described in this paper.

#### Acknowledgements

The authors would like to thank Mr. Yasuyuki Hattori of Alps Alpine Co., Ltd. for his support of this research.

#### References

- [1] S. Pavan, R. Schreier, G. C. Temes, Understanding Delta-Sigma Data Converters, Second Edition, *IEEE Press*, Jan. 2017.

- [2] T. C. Leslie, B. Singh, "An Improved Sigma-Delta Modulator Architecture", *IEEE International Symposium on Circuits and Systems*, (New Orleans, LA) May 1990.

- [3] T. Yoshitome, K. Uchimura, "Quantization Noise Reduction in 1-bit Oversampling A-to-D Converter", *IEICE General Conference in Spring*, A-126, (Japan) March 1988.

- [4] X. Li, T. Feng, L. Nengvang, S. Katayama, Jianglin Wei, H. Lin, K. Naganuma, K. Sasai, J. Saito, A. Kuwana, H. Kobayashi, "Folding ADC for Multi-bit ΔΣ AD Modulator", *IEEJ International Conference on Analog VLSI Circuits*, (Bordeaux, France) Oct. 2021.

- [5] H. Lin, N. Yamaguchi, K. Makabe, A. Kamei, H. Kobayashi, "Charge Domain Folding Analog-to-Digital Converter", *IEICE Trans.* vol. J89-C, no. 10, pp. 657-660, Oct. 2006.

- [6] C.-H. Chan, Y. Zhu, S.-W. Sin, S.-P. U, R. P. Martins, F. Maloberti, "A 5-Bit 1.25-GS/s 4x-Capacitive-Folding Flash ADC in 65-nm CMOS", *IEEE Journal of Solid-State Circuits*, vol. 48, no. 9, Sept. 2013.

- [7] W. E. M. Costa, S. A. Rodrigues, R. C. S. Freire, S. Y. Catunda, F. R. de Sousa, "8-bit Folding ADC based on Switched Capacitor", *IEEE International Instrumentation and Measurement Technology Conference*, (Minneapolis, MN) May 2013.

- [8] J. van Valburg, R. J. van de Plassche, "An 8-b 650-MHz Folding ADC," *IEEE Journal of Solid-State Circuits*, vol. 27, no. 12, pp. 1662- 1666, Dec. 1992.

- [9] H. Kobayashi, T. Mizuta, K. Uchida, H. Matsuura, A. Miura, T. Yakihara, S. Oka, D. Murata, "A High-Speed 6-bit ADC Using SiGe HBT", *IEICE Trans. Fundamentals*, vol. E81-A, no. 3, pp.389-397, March 1998.

- [10] R. J. V. Plassche, CMOS Integrated Analog-to-Digital and Digital-to-Analog Converters, *Kluwer Academic Publishers*, 2003.

- [11] A.G.W. Venes; R.J. van de Plassche, "An 80-MHz 80-mW 8-b CMOS Folding A/D Converter with Distributed Track-and-Hold Preprocessing", *IEEE Journal of Solid-State Circuits*, vo. 31, no. 12, pp. 1846-1853, Dec. 1992.

- [12] B. Nasri, S. P. Sebastian, K.-D. You, R. K. RanjithKumar, D. Shahrjerdi, "A 700 µW 1GS/s 4-bit Folding-Flash ADC in 65nm CMOS for Wideband Wireless Communications", *IEEE International Symposium on Circuits and Systems* (Baltimore, MD) May 2017.

- [13] L. Wang, M.-A. LaCroix, A. C. Carusone, "A 4-GS/s Single Channel Reconfigurable Folding Flash ADC for Wireline Applications in 16-nm FinFET", *IEEE Transactions on Circuits and Systems II: Express Briefs*, vol. 64, no. 12, pp1367-1371, Dec. 2017.

- [14] Y. Choi, S. Park, M.-K. Lee, S.-P. Nah, M. Song, "Design of a 45nm 8-bit 2GS/s 250mW CMOS Folding A/D Converter with an Adaptive Digital Error Correction Technique", *International SoC Design Conference*, (Gyeongju, Korea) Nov. 2015.

- [15] D. Park, S. Lee, M. Song, "A High Precision CMOS Folding A/D Converter with an Odd Number of Folding Blocks", *International SoC Design Conference*, (Busan, Korea), Nov. 2013.

- [16] I. Hwang, D. Kim, J.-H. Roh, M.-K. Lee, S.-P. Nah, M. Song, "An 8-b Cascaded Folding A/D Converter with a New Fully Differential Source Follower", *European Conference on Circuit Theory and Design*, (Dresden, Germany), Sept. 2013

- [17] M. Wang, T. Lin, F. Ye, N. Li, J. Ren, "A 1.2 V 1.0-GS/s 8-bit Voltage-Buffer-Free Folding and Interpolating ADC", *IEEE 55th International Midwest Symposium on Circuits and Systems*, (Boise, ID) Aug. 2012.

- [18] C. H. Vun, A. B. Premkumar, "RNS Encoding based Folding ADC", *IEEE International Symposium on Circuits and Systems*, (Boise, ID) Aug. 2012

- [19] S. D'Amico, G. Cocciolo, M. De Matteis, A. Baschirotto, "A 7.65mW 5bits 90nm 1Gs/s ADC Folded-Interpolated without Calibration", *European Conference on Solid-State Circuits* (Helsinki, Finland) Sept. 2011

- [20] A. Surano, F. Maloberti, "Design of a 12.5 GS/s 5-bit Folding A/D Converter", *First IEEE Latin American Symposium on Circuits and Systems*, (Foz do Iguacu, Brazil) Feb. 2010.

- [21] Y. Kim, J. Jeon, K. Cho, D. Kim, J. Moon, M. Song, "Design of a 7-bit 1GSPS Folding-Interpolation A/D Converter with Self-Calibration Technique", *17th IEEE International Conference on Electronics, Circuits and Systems*, (Athens, Greece) Dec. 2010.

- [22] R. C. Taft, P. A. Francese, M. R. Tursi, O. Hidri, A. MacKenzie, T. Hohn, P. Schmitz, H. Werker, A. Glenny, "A 1.8 V 1.0 GS/s 10b Self-Calibrating Unified-Folding-Interpolating ADC With 9.1 ENOB at Nyquist Frequency", *IEEE Journal of Solid-State Circuits*, vol. 44, no. 12, Dec. 2009.

- [23] Y. Nakajima, A. Sakaguchi, T. Ohkido, N. Kato, T. Matsumoto, M. Yotsuyanagi, "A Background Self-Calibrated 6b 2.7GS/s ADC with Cascade-Calibrated Folding-Interpolating Architecture", *IEEE Journal of Solid-State Circuits*, vol. 45, no. 4, pp. 7070-718, April 2010.

- [24] R. C. Taft, P. A. Francese, M. R. Tursi, O. Hidri, A. MacKenzie, T. Hoehn, P. Schmitz, H. Werker, A. Glenny, "A 1.8V 1.0GS/s 10b Self-Calibrating Unified-Folding-Interpolating ADC with 9.1 ENOB at Nyquist Frequency", *IEEE International Solid-State Circuits Conference*, (San Francisco, CA) Feb. 2009.

- [25] B. Verbruggen, J. Craninckx, M. Kuijk, P. Wambacq, G. V. der Plas, "A 2.2 mW 1.75 GS/s 5 Bit Folding Flash ADC in 90 nm Digital CMOS", *IEEE Journal of Solid-State Circuits*, vol. 44, no. 3, pp. 874-882, March 2009.

- [26] I. Bogue, M. P. Flynn, "A 57 dB SFDR Digitally Calibrated 500 MS/s Folding ADC in 0.18 μm Digital CMOS", *IEEE Custom Integrated Circuits Conference*, (San Jose, CA) Sept. 2007.

- [27] C.-C. Hsu, C.-C. Huang, Y.-H. Lin, C.-C. Lee, "A 10b 200MS/s Pipelined Folding ADC with Offset Calibration", *33rd European Solid-State Circuits Conference*, (Munich, Germany) Sept. 2007.

- [28] Y. Chen, Q. Huang, T. Burger, "A 1.2V 200-MS/s 10-bit Folding and Interpolating ADC in 0.13µm CMOS", *33rd European Solid-State Circuits Conference*, (Munich, Germany) Sept. 2007.

- [29] K. Makigawa, K. Ono, T. Ohkawa, K. Matsuura, M. Segami, "A 7bit 800Msps 120mW Folding and Interpolation ADC Using a Mixed-Averaging", *Symposium on VLSI Circuits*, (Honolulu, HI) Jun. 2006.

- [30] H. Pan, A. A. Abidi, "Signal Folding in A/D Converters", *IEEE Transactions on Circuits and Systems I: Regular Papers*, vol. 51, no. 1, pp. 3-14, Jan. 2004.

- [31] S. Fan, A. Wang, B. Zhao, "Folding and Interpolation ADC Design Methodology", *IEEE 10th International Conference on ASIC*, (Shenzhen, China) Oct. 2013.

- [32] L. Nengvang, S. Katayama, J. Wei, L. Sha, A. Kuwana, K. Naganuma, K. Sasai, J. Saito, K. Morishita, H. Kobayashi, "Generalized Leslie-Singh Architecture of 1st order Delta-Sigma AD Modulator with Different Resolutions of ADC and DAC," *5th International Conference on Technology and Social Science*, (Kiryu, Japan) Dec. 2021.

- [33] H. San, Y. Jingu, H. Wada, H. Hagiwara, A. Hayakawa, H. Kobayashi, T. Matsuura, K. Yahagi, J. Kudoh, H. Nakane, M. Hotta, T. Tsukada, K. Mashiko, A. Wada, "A Second-Order Multi-bit Complex Bandpass ΔΣAD Modulator with I, Q Dynamic Matching and DWA Algorithm," *IEICE Trans. Electronics*, vol. E90-C, no.6, pp.1181-1188, June 2007.

- [34] J.-M. Wang, S.-C. Fang, W.-S. Feng, "New Efficient Designs for XOR and XNOR Functions on the Transistor Level", *IEEE Journal of Solid-State Circuits*, vo. 29, no. 7, pp. 780- 786, July 1994.